Apple’s reliance on Taiwan Semiconductor Manufacturing Company (TSMC) has evolved from a competitive advantage into a systemic single-point-of-failure risk that threatens the enterprise's long-term valuation. While the current manufacturing partnership yields the world’s most power-efficient chips, the concentration of 90% of Apple’s advanced node production within a 100-mile radius of the Taiwan Strait creates a "Geopolitical Beta" that no amount of cash reserves can hedge. The ongoing discussions with Intel and Samsung for U.S.-based supply do not represent a mere search for a secondary vendor; they signify a fundamental shift in Apple’s procurement logic from "Efficiency-First" to "Resilience-at-All-Costs."

The Logic of Diversification: Identifying the Three Critical Risk Vectors

The transition away from an exclusive TSMC relationship is driven by three distinct but intersecting pressure points that have made the status quo untenable.

1. The Geographic Concentration Penalty

In a standard supply chain, geographic concentration reduces logistics costs. In the semiconductor industry, however, it creates a binary risk profile. The "Silicon Shield" theory—the idea that Taiwan’s importance to the global economy prevents conflict—is increasingly viewed as a fragile assumption by institutional investors. Apple’s internal risk modeling must now account for physical disruptions to the Hsinchu Science Park, whether via kinetic conflict or a naval blockade. This isn't about moving production to a cheaper location; it is about paying a "Geopolitical Insurance Premium" to ensure that the iPhone's core compute engine—the A-series and M-series chips—can be fabricated even if the Pacific trade routes are severed.

2. The Technological Stagnation Bottleneck

TSMC’s dominance in N3 (3nm) and N2 (2nm) processes has allowed Apple to maintain a performance lead over competitors. However, relying on a single roadmap limits Apple’s ability to arbitrage different transistor architectures. Intel’s "18A" process and Samsung’s "Gate-All-Around" (GAA) FET technology offer alternative paths to power efficiency. By engaging with these foundries, Apple creates a competitive auction environment, forcing TSMC to maintain aggressive pricing and innovation cycles while ensuring Apple has a "Plan B" if TSMC’s transition to High-NA EUV (Extreme Ultraviolet) lithography faces yield issues.

3. The Regulatory and Subsidy Arbitrage

The U.S. CHIPS and Science Act has fundamentally altered the capital expenditure (CapEx) math for domestic fabrication. Apple is under significant pressure from the U.S. government to act as the "anchor tenant" for domestic foundries. For Intel and Samsung, securing Apple as a customer for their U.S. plants is the ultimate validation of their "Foundry 2.0" strategies. For Apple, utilizing these facilities allows them to capture the indirect benefits of federal subsidies, potentially offsetting the higher labor and operational costs of manufacturing in Arizona or Ohio compared to Taiwan.

Deconstructing the Competitive Landscape: Intel vs. Samsung

Apple’s multi-sourcing strategy requires a granular comparison of what Intel and Samsung bring to the negotiation table. Neither currently matches TSMC’s volume or yield consistency, but both offer specific strategic utilities.

The Intel Foundry Services (IFS) Proposition

Intel’s pivot to a foundry model hinges on its 18A node. For Apple, Intel represents a unique domestic partner because its manufacturing footprint is heavily concentrated in the United States.

- Backside Power Delivery: Intel’s PowerVia technology is a potential differentiator for future M-series chips, allowing for better thermal management in thin-and-light MacBooks.

- The "American Made" Branding: There is a latent marketing and political value in an iPhone powered by an "American-made" processor, which could insulate Apple from future protectionist trade policies.

- The Yield Hurdle: The primary risk with Intel is its historical struggle to meet high-volume manufacturing (HVM) deadlines. Apple requires millions of chips per month; Intel must prove it can scale without the frequent delays that plagued its 10nm and 7nm transitions.

The Samsung Foundry Proposition

Samsung remains the only other player capable of 3nm-class production. Unlike Intel, Samsung has extensive experience in high-volume mobile SoC (System on a Chip) manufacturing.

- GAA FET Leadership: Samsung was the first to implement GAA architecture at the 3nm node. While initial yields were rumored to be low, the learning curve is flattening. Apple could leverage Samsung’s mature GAA process for lower-tier devices (like the SE line) before moving flagship production.

- Vertical Integration Risks: The complication here is that Samsung is a direct competitor in the handset market. Apple is historically hesitant to hand its proprietary designs to a rival’s manufacturing arm, fearing IP leakage or "deprioritization" during supply shortages.

The Cost Function of U.S.-Based Fabrication

Moving production to the U.S. introduces a series of economic frictions that Apple must solve through architectural efficiency or price adjustments. The delta in production costs between Taiwan and the U.S. is estimated at 30% to 50%, driven by three primary factors:

- Labor Specialization Scarcity: Taiwan has spent 40 years building a specific ecosystem of semiconductor engineers. The U.S. lacks the same density of "cleanroom-ready" talent, leading to higher recruitment and training costs.

- Supply Chain Proximity: In Taiwan, the assembly, testing, and packaging (ATP) facilities are often miles away from the fab. In the U.S., a chip finished in Arizona might still need to be shipped to Southeast Asia for packaging, unless Apple forces its partners to build domestic ATP capacity as well.

- Environmental and Permitting Overhead: The regulatory environment in the U.S. adds months, if not years, to the construction of new fabs, increasing the "Time-to-Market" risk for new chip generations.

The Architecture of a Hybrid Supply Chain

Apple is likely to adopt a "Bifurcated Fabrication" model. Under this framework, the company does not abandon TSMC but rather segments its chip portfolio based on risk and performance requirements.

- Tier 1 (Bleeding Edge): The most advanced nodes (e.g., 2nm) remain at TSMC in Taiwan for at least the next three to five years to ensure maximum performance for the "iPhone Pro" and "Ultra" lineups.

- Tier 2 (N-1 Nodes): Previous generation chips or chips for the standard iPhone and iPad models are migrated to U.S.-based Intel or Samsung fabs.

- Tier 3 (Legacy and Specialty): Power management ICs, display drivers, and secondary sensors are distributed across a global network of foundries, including those in the U.S., Europe, and Japan.

This structure allows Apple to satisfy U.S. political requirements and build a domestic "reserve" of compute power without sacrificing the performance lead of its flagship products.

Strategic Forecast: The End of the "Single Node" Era

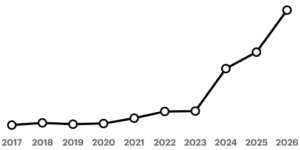

The negotiation with Intel and Samsung signals the end of the "Monolithic Foundry" era for Apple. Within the next 36 months, we should expect the first "Hybrid A-Series" chip—a processor where the compute tiles are fabricated at TSMC but the I/O or graphics tiles are fabricated by Intel or Samsung using advanced chiplet packaging techniques.

The move is not a sign of weakness in the TSMC relationship; it is a sophisticated exercise in Real Options Theory. By investing the engineering resources now to make their designs portable across different foundries, Apple is buying the "option" to switch production in the event of a catastrophe. The cost of this portability is high—re-characterizing a design for a different foundry’s process design kit (PDK) takes hundreds of thousands of man-hours—but it is the only logical move for a company whose entire product ecosystem depends on a single, vulnerable island.

Apple's final play will be the creation of a "Foundry-Agnostic" design methodology. This will involve developing internal software tools that allow Apple’s silicon team to port ARM-based designs between TSMC, Intel, and Samsung with minimal lead time. This capability will effectively turn the world's most advanced chip designers into the world's most powerful silicon commodity traders, able to shift billions in orders based on yield, price, and geopolitical stability.